SRF_AD9361_V2.0 소프트웨어 무선 주파수 단위는 AD9361 칩의 핵심입니다. 우리는 고주파 회로의 물자 그리고 impedance 던스에 따라 SRF_AD9361_V2.0 엄격히 디자인합니다. 그것은 ad9361의 성능이 손상이 없으므로 일반 사용자의 어려움을 줄여 ad9361을 사용합니다. 우리는 또한 Altera FPGA + stm32를 기반으로 완벽한 지원 마스터 및 응용 프로그램 데모 개발.

AD9361 칩은 baseband에서 고주파 (RF) 에 고성능, 높은 통합 양지향성 송수신기입니다. 칩의 풀그릴 광대역 기능은 많은 송수신기를 위한 이상적인 선택입니다. 이 장치는 RF 프런트 엔드와 혼합 신호의 유연한 기저 대역 부분을 설정하여 주파수 합성기 통합하여 프로세서를 구성 가능한 디지털 인터페이스를 제공하므로 설계 수입품을 단순화합니다. 작동 주파수 AD9361 에서 70 MHz ~ 6 GHz, 채널 대역폭 듀얼 입력 듀얼 출력 미만 200 kHz 56 MHz.

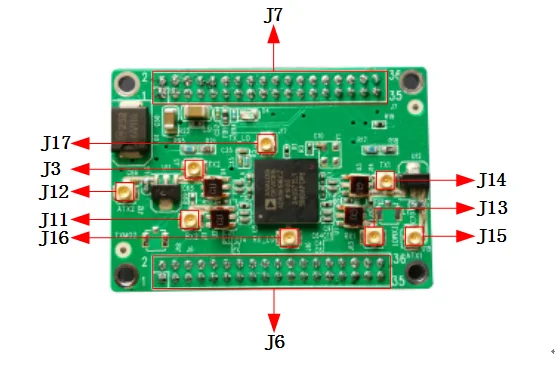

크기 RF 모듈 SRF_AD9361_V2.0 소프트웨어 라디오 35mm * 50mm 인 단일 5V.

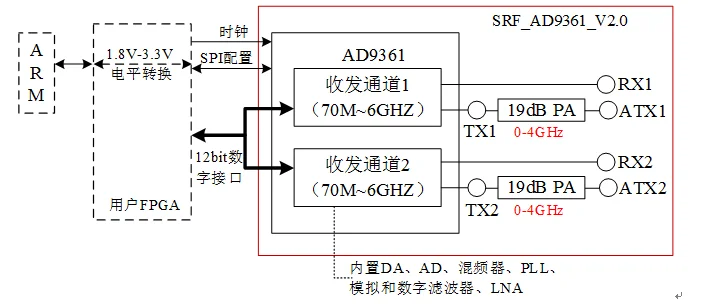

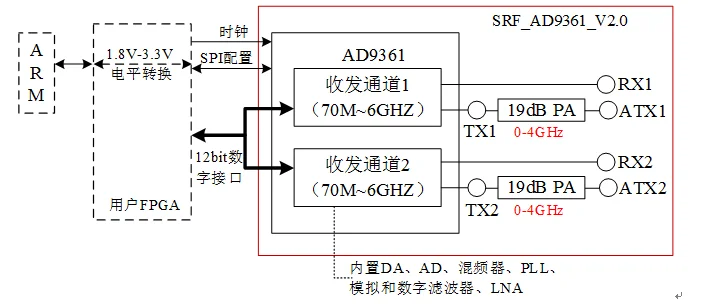

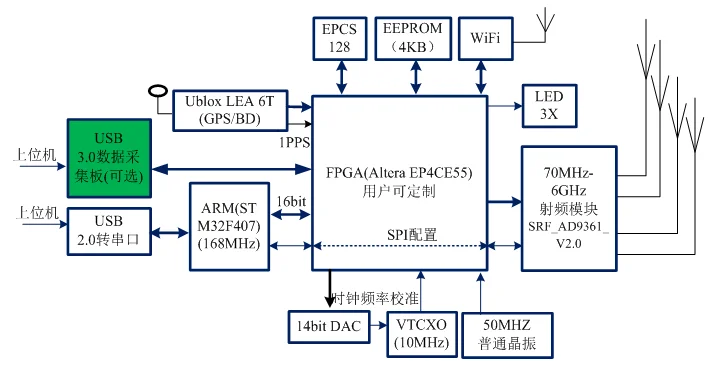

SRF_AD9361_V2.0 모듈 및 일반적인 외부 연결의 블록 다이어그램.

디지털 방식으로 측에, SRF_AD9361_V2.0 의 입력 그리고 산출은 사용자 디지털 방식으로 회로, 일반적으로 FPGA 및 팔에 직접 연결되고, 논리 수준은 1.8V. 시계 외에, 그것은 SPI 공용영역과 12 조금 사용자 기저 대역 공용영역을 포함합니다.

RF 측에, SRF_AD9361_V2.0 의 입출력 공용영역은 2개의 RF 입력 인터페이스 rx1와 rx2의 ad9361에 직접 연결되는 2개의 RF 산출 공용영역을 포함합니다, TX1 및 TX2 (TX1 및 TX2`s 신호 범위 0MHZ-6GHZ), 그리고 TX1 및 TX2 일반적으로 최대 출력 0dBm, 사용자가 가질 수 있는 전력 증폭기에 연결되기 위하여.

사용자의 작업 부하를 줄이기 위해 우리는 또한 실험실 조건에서 직접 대부분의 사용자의 사용을 촉진하기 위해 SRF_AD9361_V2.0 에 19dBm 전력 증폭기를 통합했습니다. ATX1 및 atx2는 전력 증폭의 출력입니다. 작동 범위 전력 증폭기 0-4.

그 중, J6 및 J7 모듈의 전원 및 디지털 회로 사이의 인터페이스이며, 두 개의 18*2 핀으로 구성되며 핀 사이의 간격은 2mm입니다. 어떤 ad9361의 모든 디지털 인터페이스로 이어집니다. 전원 공급 장치는 5V dc입니다.

모듈 RF 신호의 입력 및 출력은 IPEX 인터페이스를 통해 외부 인터페이스에 연결되며 다음 테이블은 각 IPEX 인터페이스의 그림입니다.

SRF_AD9361_V2.0 마더 매칭 원리

마더 보드는 SRF_AD9361_V2.0 매칭을 포함합니다:

(1) 4 디버그 LED;

(2) 일반 50MHZ 수정 발진기;

(3) GPS constrained 시간 subsystem (14bit DAC + VTCXO).

(4) SRF_AD9361_V2.0 모듈;

(5) 시간 서비스 Ublox GPS 단위;

(6) Altera EP4CE55 FPGA, 사용자 정의;

(7) STM32F407 팔, 뜨 점 가동 단위와 더불어 최대 주파수 168MHZ.

(8) USB 2 직렬 포트 모듈은 듀얼 직렬 포트를 지원하며 각 직렬 포트의 최대 비율은 9216000Baud/s입니다.

(9) wifi는 라우터 또는 일반 사용자 네트워크 카드로 구성 할 수 있습니다.

(11) 4KB EEPROM 저장 사용자 윤곽;

(12) 수동 리셋 버튼 (FPGA, FPGA 리셋 암, 암 리셋 SRF_AD9361_V2.0 모듈, 암 암 SRF_AD9361_V2.0 모듈 구성이 완료되어 FPGA 통지).

(10) 선택적 USB 3 고속 채널;

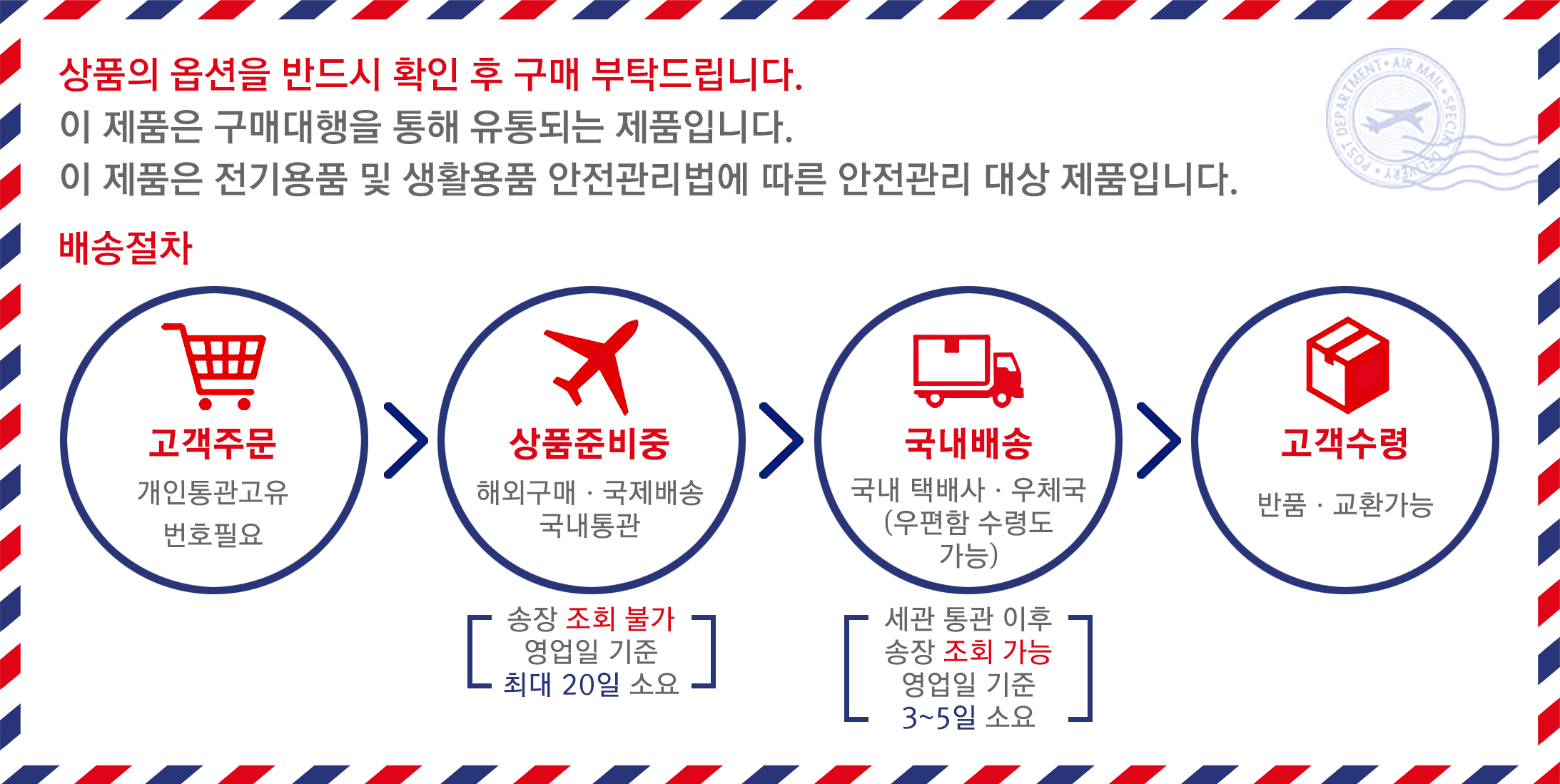

배송기간

배송기간