|

|

aHR0cDovL2ZyZWVzaGlwLmNvLmty aHR0cDovL2ZyZWVzaGlwLmNvLmty

- 데모 보드 유형: 팔

- 모델 번호: OpenEP4CE10-C Standard

- 브랜드 이름: Waveshare

- Type: FPGA Development Board

- Designed for: ALTERA Cyclone IV series

- Mother board: DVK600

- Core board: CoreEP4CE10

ALTERA Cyclone IV 시리즈 용으로 설계된 FPGA 개발 보드는 EP4CE10 온보드를 특징으로하며 다양한 표준 인터페이스를 통합하여 주변 확장이 매우 쉽습니다.

개@@ 요OpenEP4CE10-C마더 보드로 구성된 FPGA 개발 보드입니다.DVK600그리고 FPGA 코어 보드CoreEP4CE10. OpenEP4CE10-C 특정 응용 프로그램에 대한 다양한 옵션 액세서리 보드를 사용하여 추가 확장을 지원합니다. 모듈과 개방형 디자인은 ALTERA Cyclone IV 시리즈 FPGA 장치로 애플리케이션 개발을 시작하는 데 이상적입니다. OpenEP4CE10-C Nios II 프로세서로 디자인을 쉽고 빠르게 시작할 수 있습니다. 마@@ 더 보드@@ 에 뭐@@ 가 있는@@ 지

- FPGA CPLD 코어 보드 커넥터:온보드 FPGA CPLD 칩을 통합하는 코어 보드를 쉽게 연결할 수 있습니다.

- 8I/Os_1 인터페이스,액세서리 보드/모듈 연결 용

- 8I/Os_2 인터페이스,액세서리 보드/모듈 연결 용

- 16I/Os_1 인터페이스,액세서리 보드/모듈 연결 용

- 16I/Os_2 인터페이스,액세서리 보드/모듈 연결 용

- 32I/Os_1 인터페이스,액세서리 보드/모듈 연결 용

- 32I/Os_2 인터페이스,액세서리 보드/모듈 연결 용

- 32I/Os_3 인터페이스,액세서리 보드/모듈 연결 용

위의 모든 I/O 인터페이스: - USART, I2C, SPI, PS/2 등으로 시뮬레이션 가능.

- 프레임, 플래시, USB, 이더넷 등과 같은 구동 장치가 가능합니다.

9. SDRAM 인터페이스 - SDRAM 액세서리 보드 연결 용

- FPGA CPLD 핀 확장 커넥터로도 작동

10.LCD 인터페이스,LCD22, LCD12864, LCD1602 연결 용 11.단선 인터페이스:온도 센서 (DS18B20), 전자 등록 번호 (DS2401) 등과 같은 단선 장치 (to-92 패키지) 에 쉽게 연결할 수 있습니다. 12.5V DC 잭 13.조이스틱:다섯 가지 위치 14.부저 15.전위차계:LCD22 백라이트 조정 또는 LCD12864, LCD1602 대비 조정 16.전원 스위치 17.부저 점퍼 18. 일@@ 선 점@@ 퍼 19.조이스틱 점퍼 점퍼 17-19 용: - 예시 코드에서 사용되는 I/os에 연결할 점퍼 짧게

- 점퍼 와이어를 통해 다른 맞춤형 핀에 연결하려면 점퍼를 엽니 다.

DVK600 은 다양한 코어 보드를 지원하므로 일부 인터페이스는 특정 코어 보드에 연결하는 동안 연결되지 않고 쓸모가 없을 수 있습니다. CoreEP4CE10 에는 무엇이 있습니까?

- EP4CE10F17C8N:다음과 같은 특징을 갖춘 ALTERA Cyclone IV FPGA 장치:

- 작동 빈도:50MHz

- 작동 전압:1.15V ~ 3.465V

- 패키지:BGA256

- I/Os:164

- 레:10K

- RAM:414kb

- PLLs:2

- 디버깅/프로그래밍:JTAG 지원

- AMS1117-3.33.3V 전압 조정기

- AMS1117-2.52.5V 전압 조정기

- AMS1117-1.21.2V 전압 조정기

- EPCS16,코드 저장용 온보드 직렬 플래시 메모리

- 전원 표시기

- Led

- 리셋 버튼

- NCONFIG 버튼:FPGA 칩을 다시 구성하기 위해 전력 재설정과 동일합니다.

- 50M 활성 크리스@@ 탈

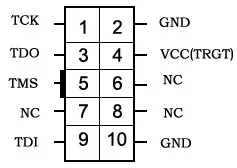

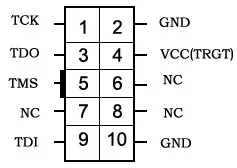

- JTAG 인터페이스:디버깅/프로그래밍 용

- FPGA 핀 확장기,추가 확장을 위해 확장 커넥터에서 VCC, GND 및 모든 I/O 포트에 액세스 가능

사진

참고: OpenEP4CE10-C 프로그래밍/디버깅 기능을 통합하지 않습니다. 프로그래머/디버거가 필요합니다. 예OpenEP4CE10-C FPGA 개발 보드에는 지원되는 주변 장치에 대한 다양한 예시 코드가 함께 제공되어 자체 애플리케이션을 빠르게 개발할 수 있습니다.

디버깅/프로그래밍 인터페이스OpenEP4CE10-C FPGA 개발 보드는 프로그래밍/디버깅을 위한 JTAG 인터페이스를 통합합니다. JTAG 신호 이름 및 설명

JTAG 헤더 핀아웃

개발 리소스사용자 가이드 cd에는 다음과 같이 나열된 개발 리소스가 포함되어 있습니다. - 관련 소프트웨어 (Quaters II, NIOS II 등)

- 데모 코드 (Verilog, VHDL 및 NIOS II C)

- 회로도 (PDF)

- FPGA 개발 문서 (데이터 시트 등)

위키: 패키지 포함- OpenEP4CE10-C 개발 보드

- 4 핀 와이어 x 2

- 2 핀 와이어 x 2

- USB 전원 케이블 x 1

|

|

|

|

|

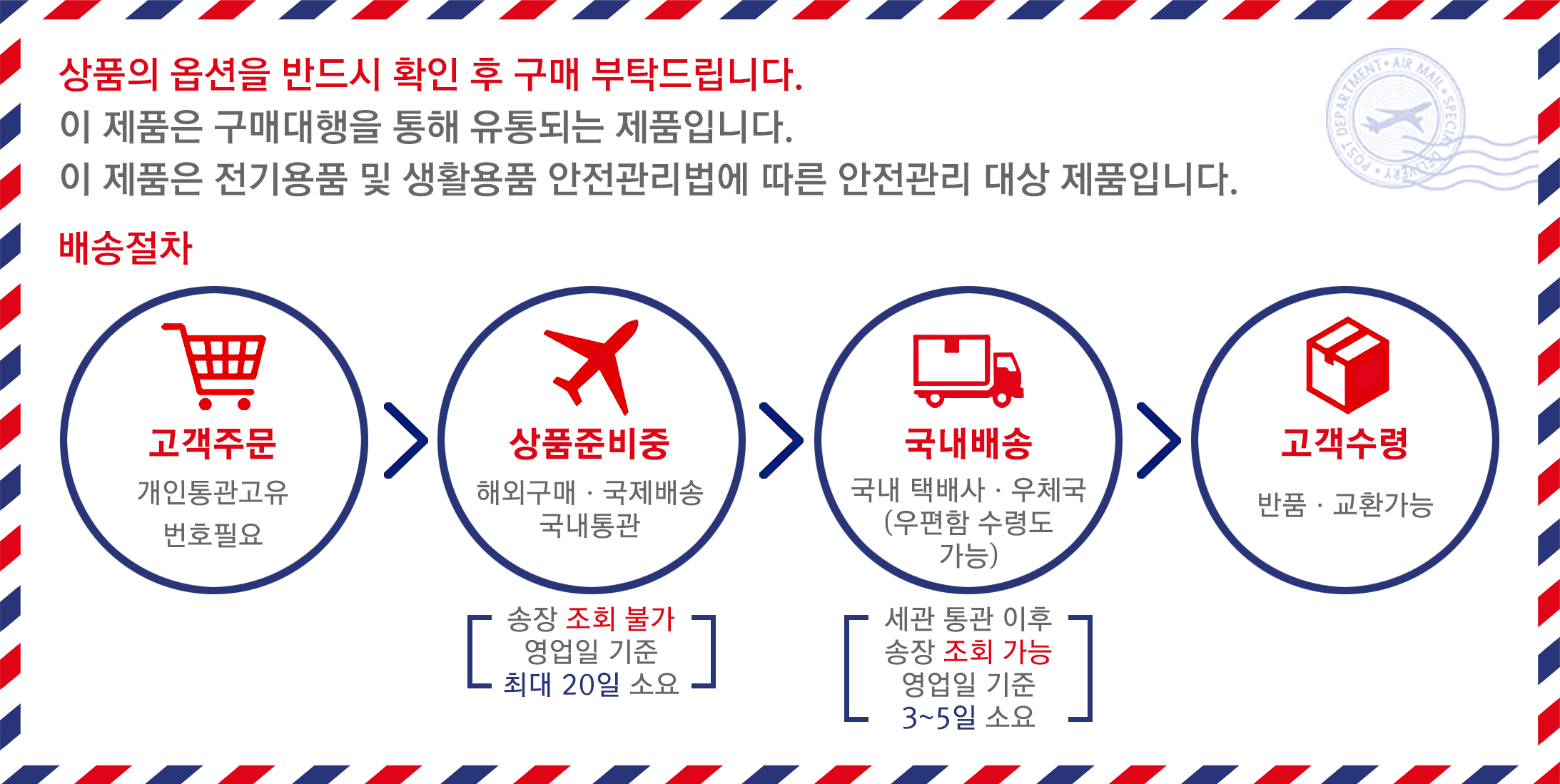

배송기간

배송기간